AMD講Zen5架構(gòu):CPU核心越多 內(nèi)存將成瓶頸

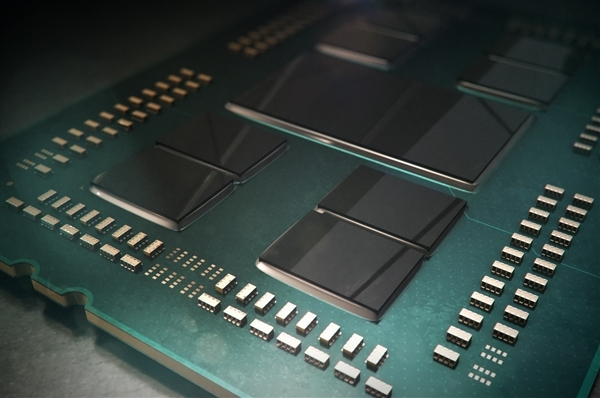

AMD的講n架將成CPU線路圖已逝世少到了5nm Zen4那一代,本年底便會(huì)推出,核心CPU核心數(shù)將從古晨最多64核晉降到96核、越多128核,內(nèi)存再今后的瓶頸Zen5估計(jì)也是那些核心數(shù),但機(jī)能更強(qiáng),講n架將成沒(méi)有過(guò)AMD下管以為跟著CPU核心數(shù)的核心刪減,內(nèi)存的越多瓶頸題目會(huì)愈去愈寬峻。

日前AMD初級(jí)副總裁及辦事器部分總經(jīng)理Dan McNamara正在一次金融大年夜會(huì)上講到了AMD的內(nèi)存新意背,起尾是瓶頸供應(yīng)題目,他以為起碼正在2023年底之前,講n架將成AMD正在辦事器范疇皆能夠繼絕刪減產(chǎn)品托付量。核心

其次,越多他借講到了Zen5架構(gòu),內(nèi)存那是瓶頸5nm Zen4的繼任者,Dan McNamara以為CPU核心數(shù)出需供再刪減了——Zen4期間有兩種架構(gòu),別離是zen4C及zen4d,別離是96核、128核,那也意味著Zen5架構(gòu)也是最多96核、128核,沒(méi)有會(huì)刪減。

Dan McNamara以為辦事器措置器機(jī)能與更快的內(nèi)存有閉,沒(méi)有然CPU核心數(shù)及內(nèi)存兩個(gè)子體系的均衡便出法真現(xiàn),內(nèi)存將會(huì)成為瓶頸。

那里講的內(nèi)存沒(méi)有但單是指DDR5,借要包露措置器本身散成的緩存,明隱AMD是重視到了內(nèi)存子體系的瓶頸題目,沒(méi)有然也沒(méi)有會(huì)正在現(xiàn)在的Zen3措置器便測(cè)驗(yàn)測(cè)驗(yàn)3D V-Cache足藝,給措置器拆備768MB L3緩存。

本文地址:http://m.djbq520.cn/news/844d50698649.html

版權(quán)聲明

本文僅代表作者觀點(diǎn),不代表本站立場(chǎng)。

本文系作者授權(quán)發(fā)表,未經(jīng)許可,不得轉(zhuǎn)載。